You can see more details here: http://www.neo-geo.com/forums/showthrea ... VS-and-AES

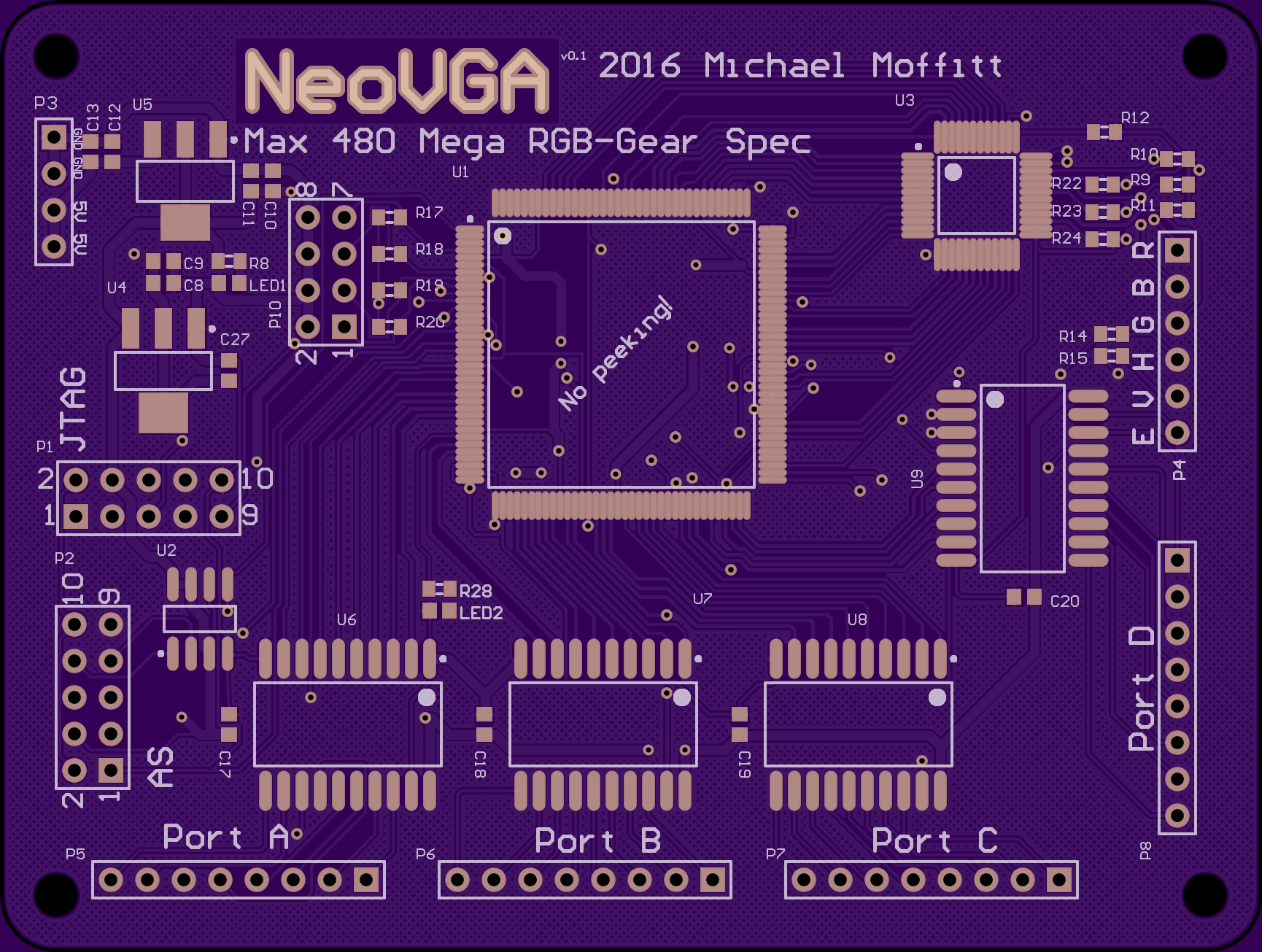

In short, this began as an FPGA taking the pixel bus information from a Neo-Geo board, and digitally line doubling it to 480p over VGA. The advantage of the simple method here is that it does not lag - it operates in a very similar mode as the XRGB2, but the main difference is that rather than having an ADC with a fixed sampling rate (or with clock recovery) this is running in lockstep with the original system's pixel clock, so the resulting image is perfect.

SUPPORTED VIDEO MODES:

-480p VGA

-480p YPbPr / Component

-240p RGB (sync on pin 13 of the VGA plug)

-240p YPbPr

The system can switch between these on the fly. The board is designed to sit inside the AES console or MVS arcade machine, mounted gently on or near the motherboard.

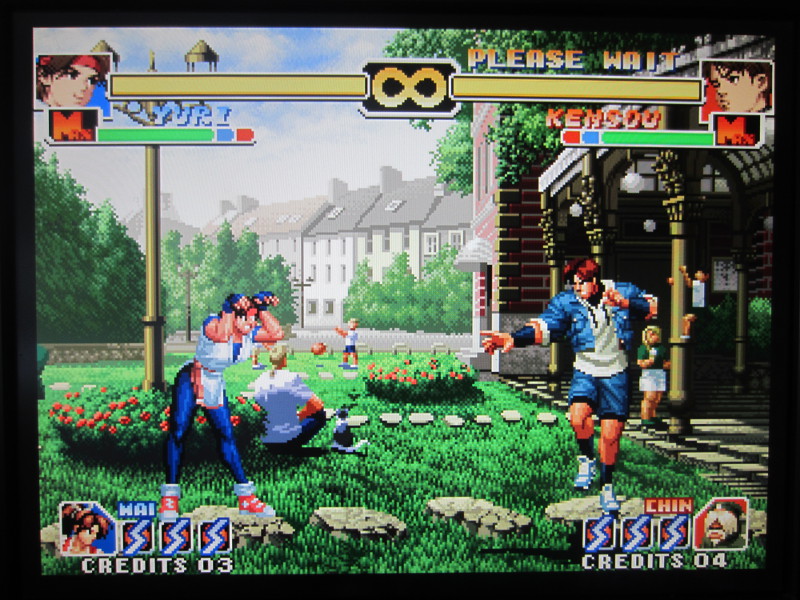

This is it running on an old NEC 20" LCD monitor:

Here it is on a PC CRT monitor (with one of my scanline settings):

As you can see scanline generation is built-in. If you want some high-res CRT porn of how it looks on a nice CRT (like some of the Sony GDM series monitors) check this out:

Anyway, since then, I've made a few alternate firmwares for it, including CPS1/2 (CPS3 might be possible?) and Williams arcade hardware (Robotron, Joust, etc). I am also working on a Sega Genesis variant, but that will be a lot more development work. I designed the PCB to have a bunch of 5V-tolerant IO ports on it so as I gain access to new arcade hardware I can see about adding support. Most of these old arcade games have the entire pixel bus just sitting there, waiting to be tapped in to. I would not be surprised if >80% of '90s and older arcade games could be supported with this.

I've just submitted my first PCB design to be fabricated for testing:

I'll keep this thread and the old one updated as things progress.

| My games -

| My games -