The new model improves almost all aspects of the original design and incorporates several new features which has been requested by community over the years. A preliminary block diagram, concept pictures and summary of key improvements are presented below.

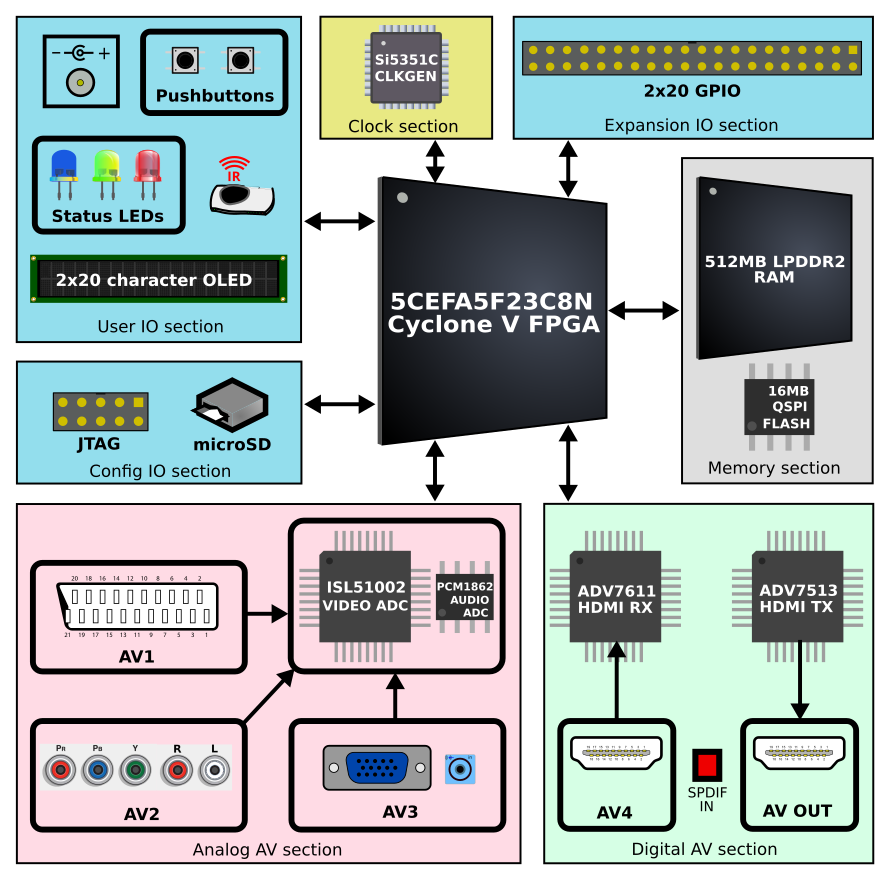

Block diagram:

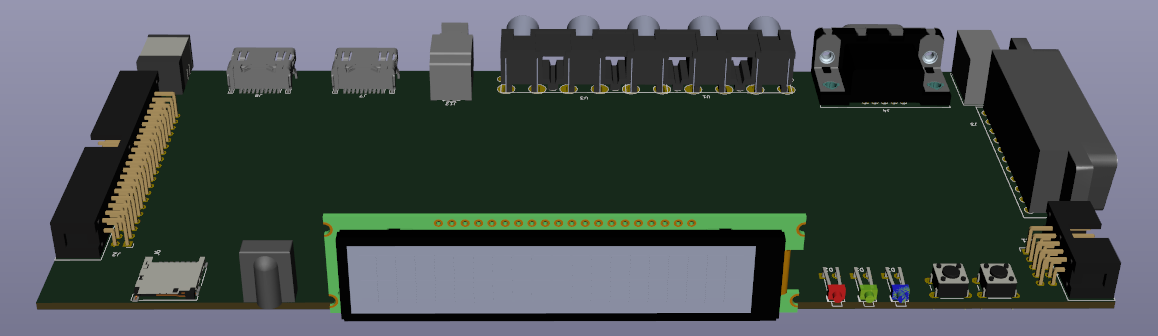

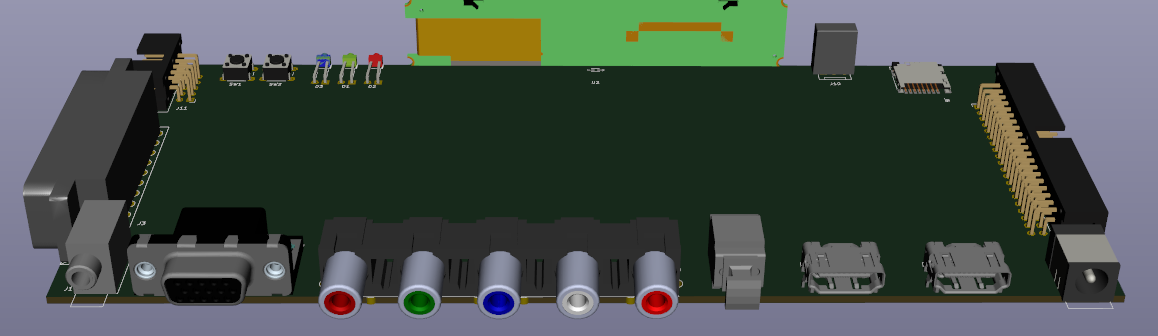

Concept pictures:

Highlights of the new design:

ISL51002 video ADC:

* improved sync processing robustness

* reduced sampling jitter with DPLL

* fine-grained video LPF

* automatic sampling phase adjustment

Cyclone V FPGA (5CEFA5F23C8N):

* higher performance and more resources

* hard memory controller

* large number of IOs

Clocking and memory improvements:

* Si5351C clock generator for accurate output pixel clock generation (framelock or free-running)

* 512MB LPDDR2 RAM and 16MB QSPI flash

New AV inputs:

* HDMI

* SPDIF (optical)

2x20 pin GPIO connector for future expansion possibilities such as:

* composite & s-video input module

* secondary video output (e.g. VGA) module

* latency tester interface module

* game controller port module (for using OSSC Pro as a dedicated FPGA console)

The processing modes enabled by the HW can be split roughly into three types:

1. Pure line multiplier

* both active and blanking lines multiplied - basically what original OSSC does

* simplest mode with least latency

2. Adaptive line multiplier

* visible lines are multiplied but horizontal & vertical total matched to standard timings

* high compatibility with minimal latency overhead (1-30 lines typically)

* enables some new output configurations such as 4x240p/2x480p in standard 1080p frame

3. Scaler

* higher flexibility via LPDDR2 utilization

* HQ deinterlacing

* non-integer scaling

* rotation

* refresh rate conversion

It will take time until all the features get implemented, but release can be expected once the HW is complete and a sufficient number of new features are available and verified. As a thanks to community's support for the first project, upcoming prototypes of the new model will be sent to the guys who have contributed most on the original OSSC firmware. New developers are also welcome as the project is large enough to enable different implementation areas for several people. For DIY-builders and those who can't wait for the final HW, a small add-on PCB compatible with a couple Terasic FPGA dev boards (DE10-Nano, DE2-115) is in works and available soon. Together with the parent dev board, it can be used to implement a subset of the functionality presented above.

UPDATE 10/2020: Prototype round delayed due to last minute changes and lead time issues, current ETA 11/2020

UPDATE 12/2020: Prototypes received, testing ongoing

UPDATE 06/2021: PCB is ready for production, other HW is being finalized

UPDATE 01/2022: Production postponed due to component shortages

UPDATE 05/2022: Production of DExx-vd_isl boards started while waiting for component market to normalize for OSSC Pro launch

UPDATE 12/2022: Availability of a couple key components still remains weak with no near-term improvement in sight

UPDATE 10/2023: First batch is being manufactured and should be available 11/2023